# Latest Advancements in Motor Hardware-In-the-Loop Simulation (HILS) based on JMAG-RT

# Simon Abourida Opal-RT Technologies, Inc.

#### Abstract:

Motor HILS (Hardware-in-the-loop simulator) has been recognized for many years now as an essential design and testing tool of motor drives, for increased product reliability, shorter time to market and lower total design cost. However, there remained many needs of the motor HILS to be addressed. Among these needed features are: more accurate models, more powerful simulators with distributed processing, etc.

Finite-Element Analysis based motor HILS, resulting from the integration of JMAG-RTR tool with RT-LABR simulator, addresses and fulfills these requirements. JMAG-RT-based Motor HILS of a complete permanent magnet synchronous motor drive can be conducted today on RT-LAB HILS at sub-microsecond time steps on powerful new FPGA resulting in unprecedented simulation accuracy.

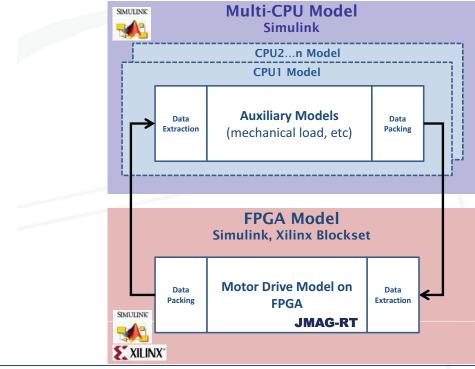

And the integration with multi-processor platform yields a full motor HILS with high accurate motor model, ultra-fast drive simulation and distributed multi-rate simulation enabling the integration of other parts of the designed system (electrical, mechanical, hydraulic, etc), for a complete system HILS.

The presentation discusses all these items and describes the latest advancements in motor HILS.

# Latest Advancements in Motor Hardware-In-the-Loop Simulation (HILS) based on RT-LAB & JMAG-RT

#### JMAG Users Conference 2010 Simon Abourida

Date: 2010-11-10

#### **Abstract**

- Motor HILS (Hardware-in-the-loop simulation)

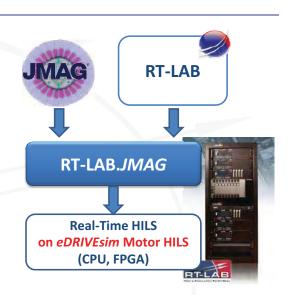

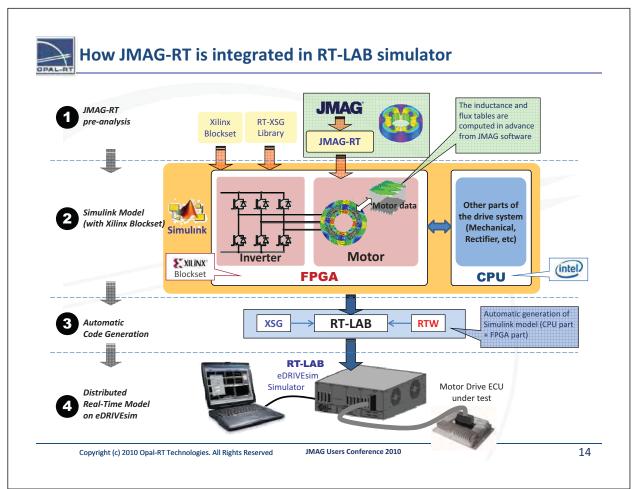

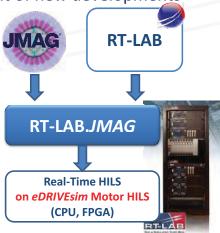

- Integration of JMAG-RT® tool with RT-LAB® HILS simulator

- → motor HILS at ~ 1 us

- All types of faults on the motor drive supported (open/short-circuit)

- Multi-processor HILS platform→ a large system HILS

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

#### **Outline**

- A. Overview

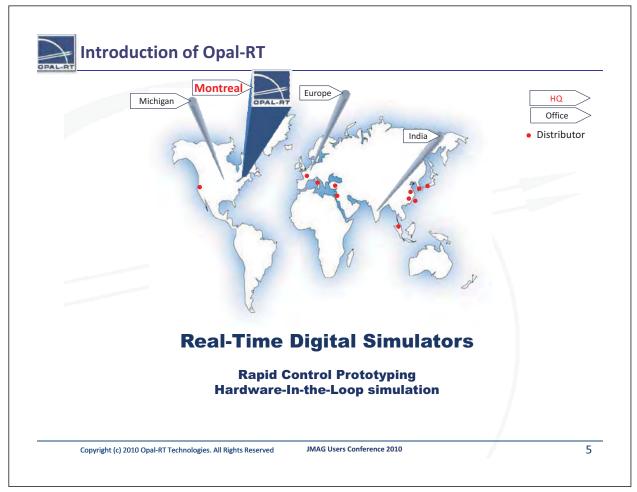

- Introducing Opal-RT

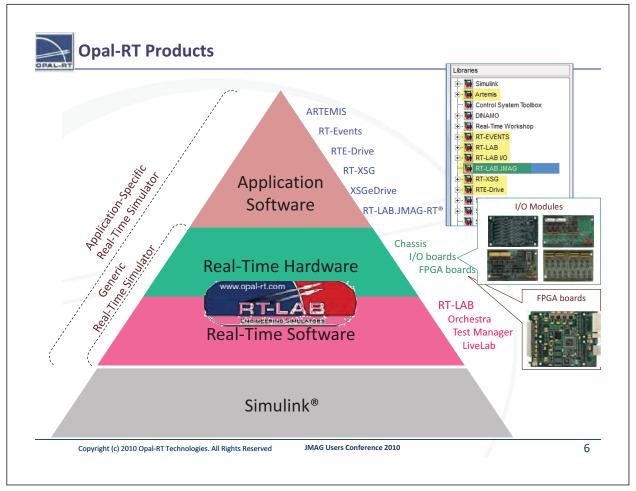

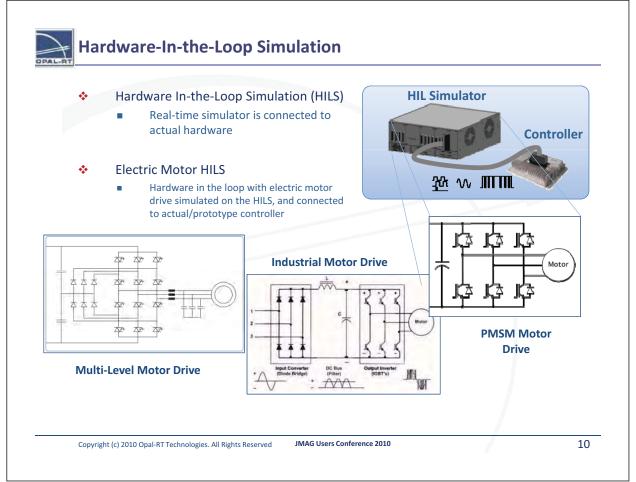

- ★ Hardware-In-the-Loop Simulation → RT-LAB

- Finite-Element Analysis→ JMAG-RT

- JMAG-RT & RT-LAB

- **B.** Latest Advancements

- FPGA-based Motor HILS

- Features

- Fault modes

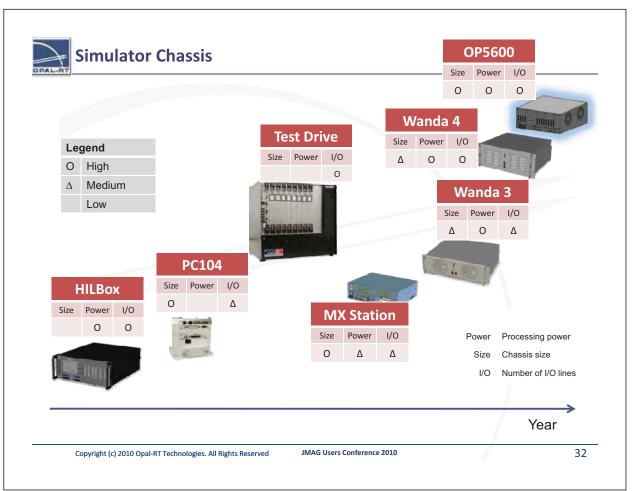

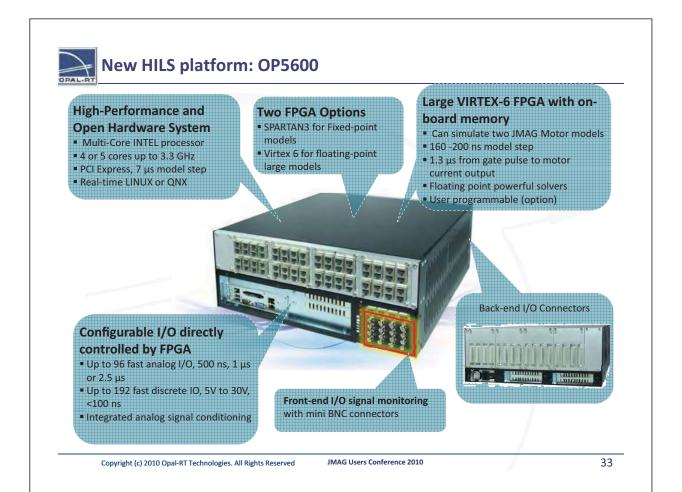

- HILBox OP5600

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

3

Latest Advancements in Motor Hardware-In-the-Loop Simulation (HILS) based on RT-LAB & JMAG-RT

# A. OVERVIEW

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

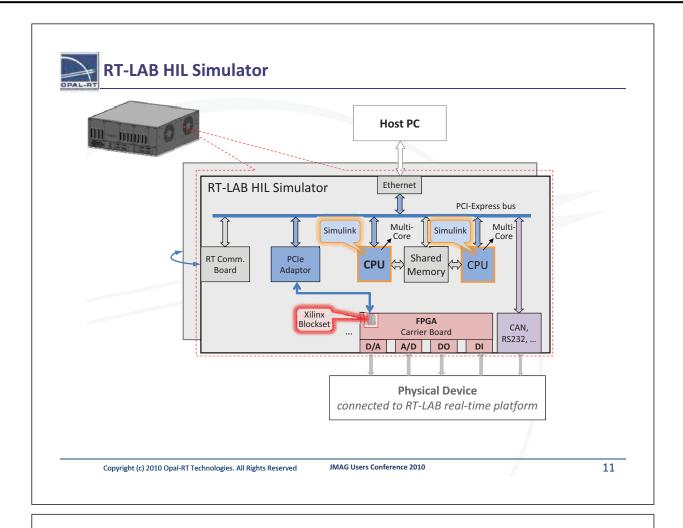

# **RT-LAB HIL Simulator - Features**

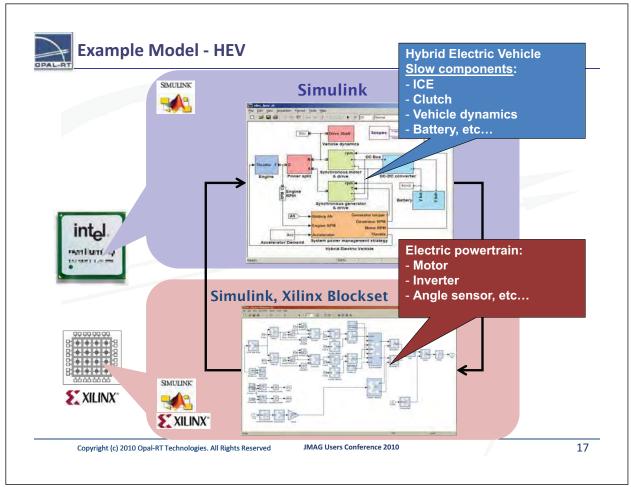

- PC- & FPGA-based, multi-processor, multi-core

- Simulink model-based design

- Inputs/Outputs:

- Ultra-fast FPGA-based I/Os

- Digital, analog, PWM, encoders, resolvers, etc

- Real-Time OS (Real-Time Linux, QNX)

- Very fast sample times:

- Intel & AMD Processor Target: 5 10 μs

- Xilinx FPGA Target: 0.2 2.0 μs (Model update at: 5-20 ns)

#### **Features**

- Speed: Very small simulation step down to 0.25 us (FPGA), 8 us (PC processor)

- Scalability: Support of complex simulations with modular <u>distributed</u> processing:

- On multi-processors

- On multi-cores

- On multiple FPGA boards

- Accuracy:

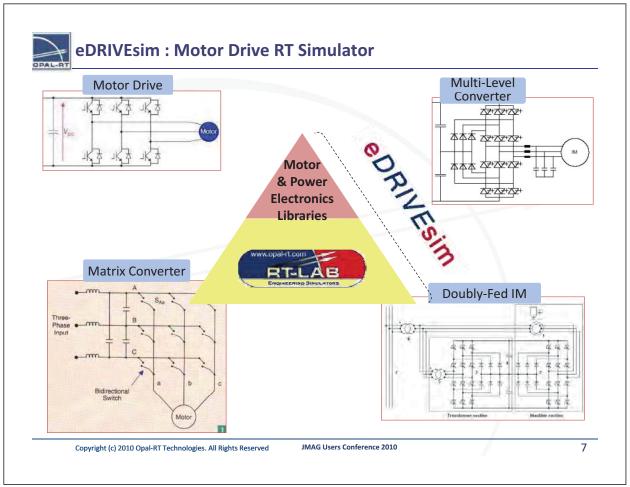

- Different types of electric motors (PMSM, BLDC, IM)

- Inverter dead-time, Regenerative braking

- Fault conditions and modes

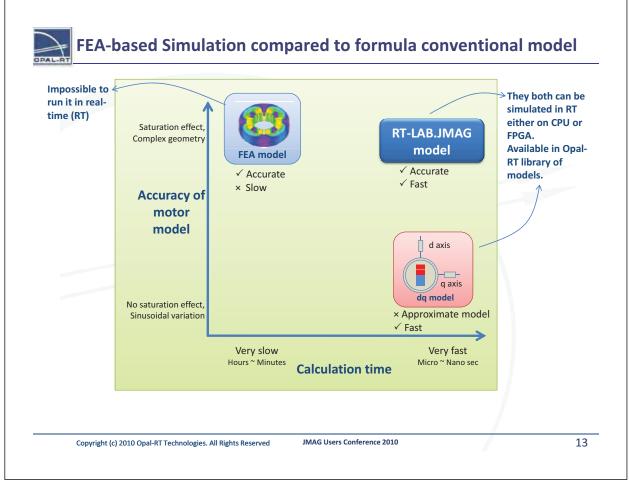

- Modeling of saturation effects of magnetic material using Finite Element-based model in real-time (from JMAG-RT)

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

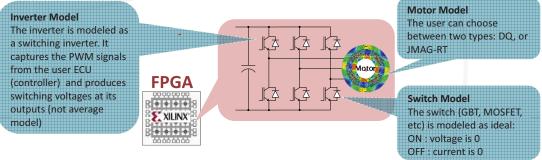

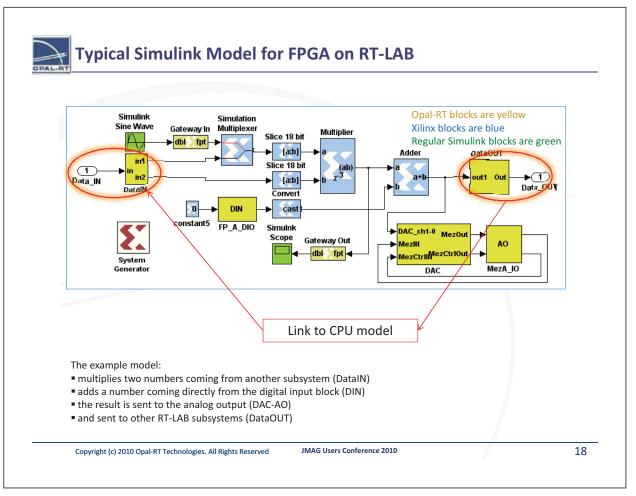

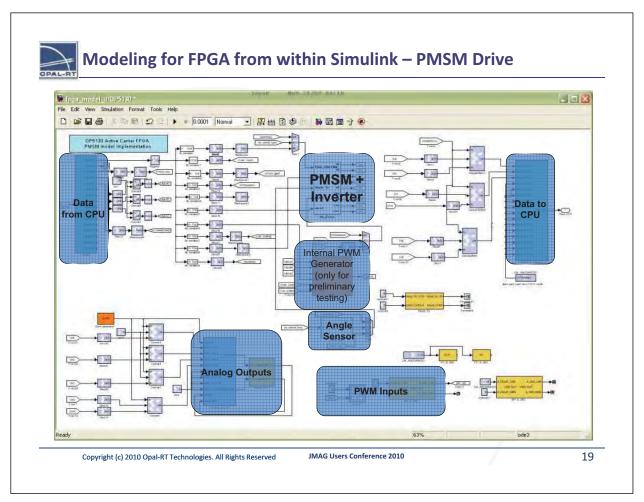

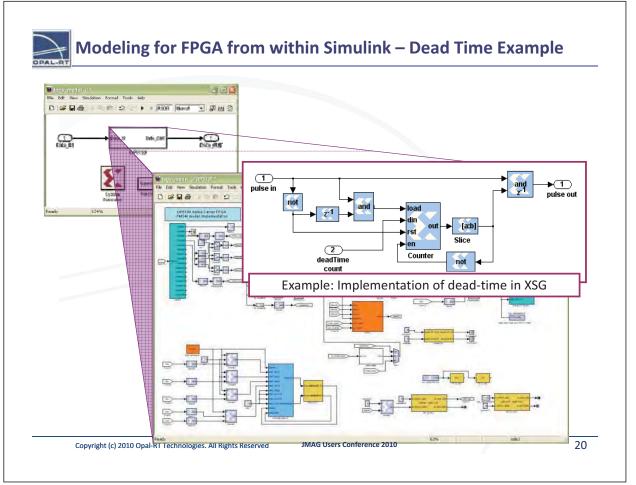

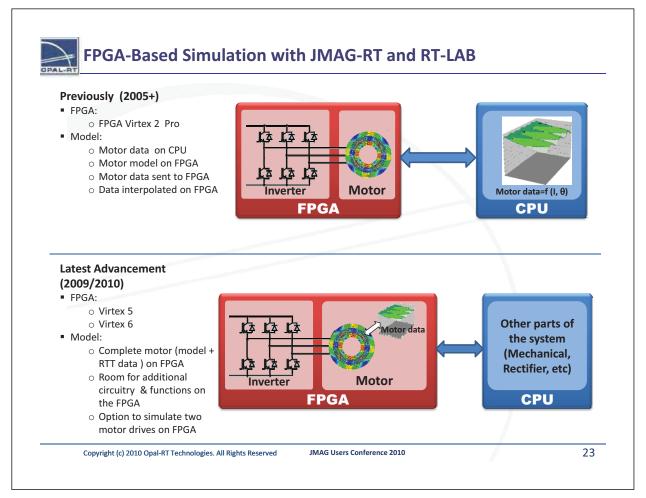

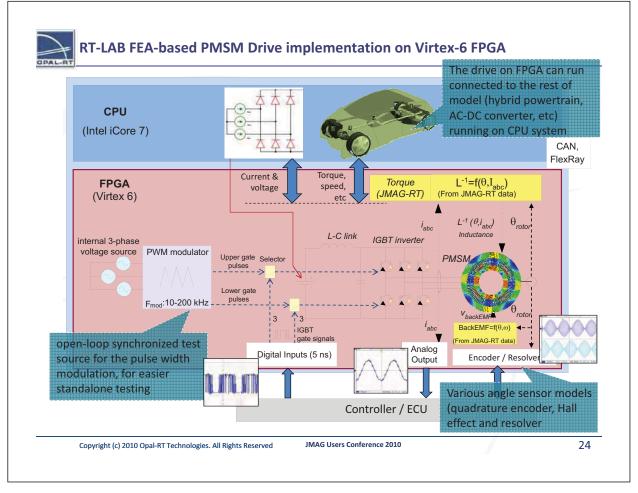

#### **FPGA-Based motor HILS - Description**

- Complete motor drive:

- DC link, inverter, motor

- Internal PWM generator for autonomous testing

- PWM input capture and analog outputs

- Different angle sensors emulated: Incremental, Resolver, Hall effect

- Mechanical load can be easily added on CPU

- Motor model is based on JMAG-RT®

- Implemented on powerful Virtex 6 FPGA (also Virtex 2, and Virtex 5)

- Completely designed in Simulink® and Xilinx® Blockset

- No VHDL coding; and is easily modifiable by the user

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

15

#### Model Structure in RT-LAB

${\it Copyright (c) 2010 \ Opal-RTTechnologies. \ All \ Rights \ Reserved }$

JMAG Users Conference 2010

# **Motor Drive Library for FPGA**

- Opal-RT delivers a library of advanced motor drive models.

- This library of FPGA models contains :

- PMSM machine

- BLDC machine

- JMAG-based PMSM model

- 3-phase inverter model

- Internal PWM modulator with dead-time

- Resolver encoder, resolver-to-digital decoder

- Quadrature encoder

- Hall effect sensor

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

21

Latest Advancements in Motor Hardware-In-the-Loop Simulation (HILS) based on RT-LAB & JMAG-RT

# **B. LATEST ADVANCEMENTS**

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

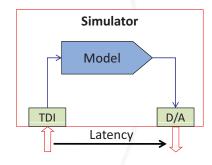

#### **Motor Simulator Timings & Latency**

- Timing The PMSM drive model:

- runs with an equivalent **5 nanosecond** time step (200 MHz Virtex-6 FPGA card)

- has an update of 200 300 nanoseconds (PMSM machine DC-link and inverter)

- The motor drive is directly connected to digital inputs and analog outputs with 1 microsecond settling time on the FPGA card and has a resulting total hardware-inthe-loop latency of 1.2 - 1.5 microseconds

- Total Delay "from Timed Digital Inputs to Analog Outputs" \*

- Motor drive HILS: "from Gate Signal Inputs to Current Outputs" \*\*

- Latency (maximum values)

- **CPU Target**  $\rightarrow$  2.Ts - 3.Ts

- $\rightarrow$  1.2 1.3 µs **FPGA Target** (Ts: Time Step)

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

**JMAG Users Conference 2010**

25

# **Total Latency Measurement** Delay: «PWM in-to-Current out» (1.3-Measurement of delay from PWM transition to current change

About 1.5usec About 1.3usec **PWM** nput Current PWM input output CH2 / 5.20V CHT 100mV CH2 10.0V M 2.50,us

CH3 10,0V

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

CH1 500mV CH2 10.0V M 500,us

**JMAG Users Conference 2010**

CH4 10.0V

26

10.0777kHz

### **Additional Features and Modes in RT-LAB HILS**

The HIL simulation of two motor drives on the same FPGA board (Virtex 6) is supported

Regenerative breaking is supported (when electric braking energy is sent back from the PMSM back to the battery through the inverter)

The DC link in front of the inverter can be modeled with its Inductance and capacitance equivalent circuit

LC Circuit

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

27

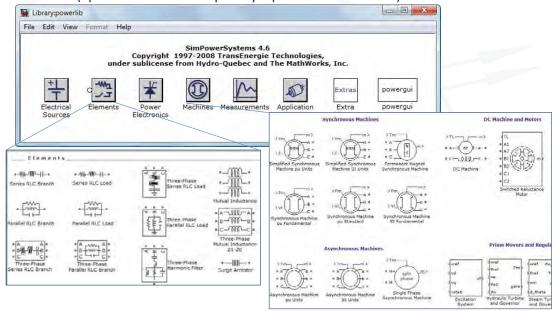

# Additional Features in RT-LAB HILS → SimPowerSystems

Optional Interface with SimPowerSystem (Special solver developed by Opal-RT for real-time)

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

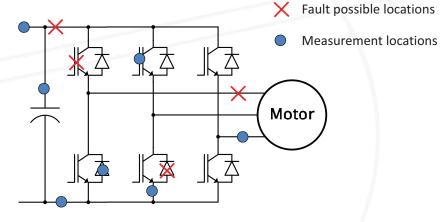

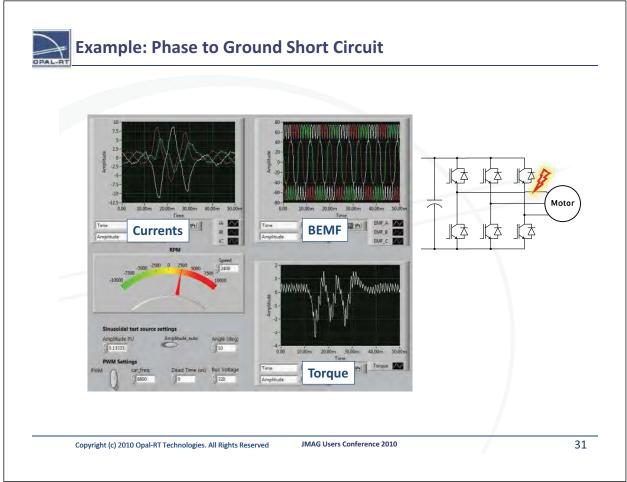

# **Fault modes**

- The PMSM drive model support all these types of faults:

- IGBT open/short-circuit

- Diode open/short-circuit

- Motor stator short-circuits (phase-GND, phase-phase)

- DC-link short-circuit

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

29

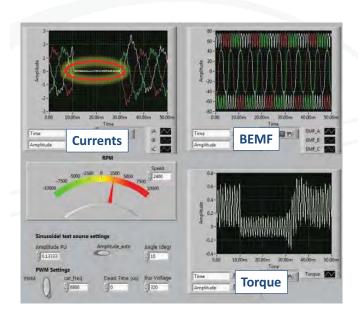

# **Example: Open Stator Test**

Motor

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

#### **Conclusions**

- The combination of RT-LAB & JMAG-RT gives the user the most advanced motor HILS

- JSOL and Opal-RT are pioneers in answering the needs of the motor drive design and testing by continuously being at the forefront of new developments

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010

# References

- IEA Status Overview of Hybrid and Electric Vehicle technology (2007)

- JSOL Corporation (<a href="http://www.jmag-international.com/">http://www.jmag-international.com/</a>)

- The Mathworks (<a href="http://www.mathworks.com/">http://www.mathworks.com/</a>)

- U.S. Department of Energy

- DENSO CORPORATION

(http://www.globaldensoproducts.com/dcs/epss/index.html)

Copyright (c) 2010 Opal-RT Technologies. All Rights Reserved

JMAG Users Conference 2010